Direct Memory Access (DMA) is a technique used in computer systems to facilitate data transfers between memory and I/O devices without the direct involvement of the microprocessor. There are three main types of data transfers in a microcomputer system:

- Data transfer between microprocessor and memory (Ex. using LDA and STA instructions);

- Data transfer between microprocessor and I/O ports (Ex. using IN and OUT instructions);

- Data transfer between memory and I/O ports (DMA data transfer).

Need for DMA

- DMA significantly boosts data transfer efficiency compared to programmed I/O methods.

- It is essential for high-speed I/O devices like hard disks and floppy disks.

- DMA facilitates the handling of large data transfers, even with slower devices such as A/D converters.

- By offloading data transfer tasks, DMA frees up the CPU for other tasks, improving overall system performance.

- DMA ensures data integrity by preventing loss or overwriting during transfers.

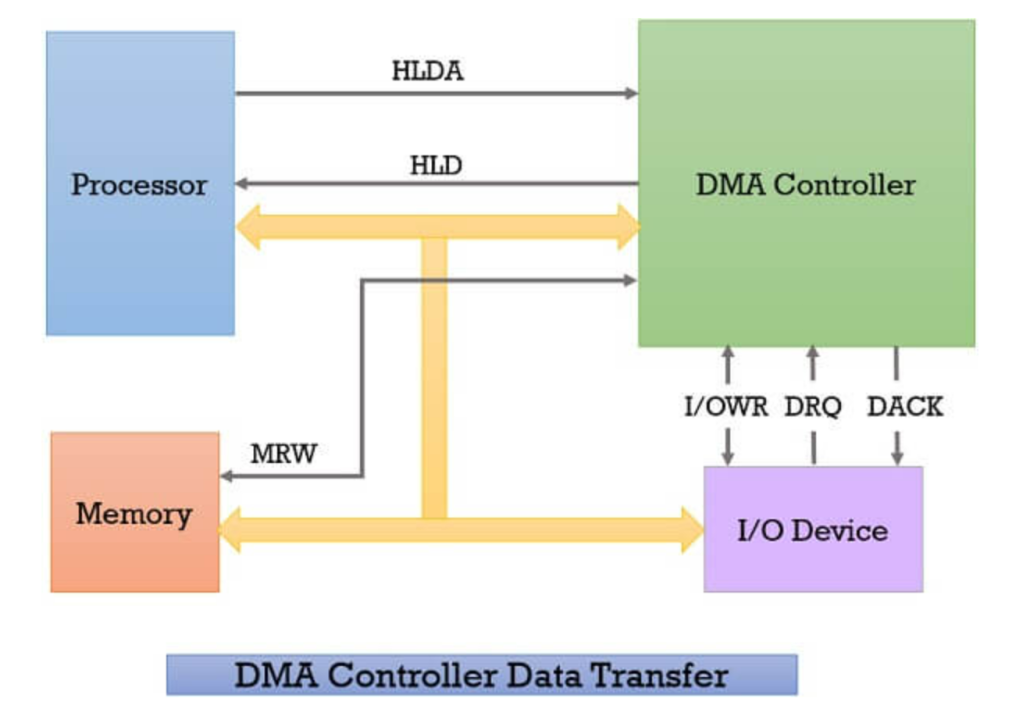

Operations of DMA

- Initially, the CPU maintains control over the system buses, managing data transfer and processing tasks.

- When a peripheral device requires data transfer, it sends a DMA request (DRQ) to the DMA controller.

- Upon receiving the DRQ signal, the DMA controller requests control of the buses by sending a Hold Request (HRQ) to the CPU.

- The CPU acknowledges the request by sending a Hold Acknowledge (HLDA) signal to the DMA controller, releasing control of the buses.

- With control over the buses, the DMA controller initiates the data transfer process, loading appropriate control signals onto the buses for the desired operation.

- The DMA controller sends acknowledgment signals (DACK) to the peripheral device, indicating readiness for data transfer.

- The peripheral device transfers data directly to the specified memory location, facilitated by the DMA controller. This bypasses CPU involvement, enhancing system efficiency.

- Upon completing the data transfer, the DMA controller generates an interrupt to notify the CPU of the transfer’s completion.

- The DMA controller relinquishes control of the buses back to the CPU, allowing it to resume normal operation.